#### EEE598D: Analog Filter & Signal Processing Circuits

Instructor: Dr. Hongjiang Song

Department of Electrical Engineering Arizona State University

#### Tuesday February 12, 2002

Today: Introduction to SC Circuits

- SC Circuit Fundamental

- Charge Redistribution Analysis

- Transfer Function

- A SC circuit operates as a DT signal processor.

- Most easily analyzed using the z-transform.

- Require anti-aliasing and smoothing filters.

- The technique has become extremely popular due to:

- Accurate frequency response (determined by capacitance ratios that can be set with an accuracy of 0.1% or better)

- Good linearity and dynamic range

- Applications:

- Filters, gain-stages, oscillators and modulators.

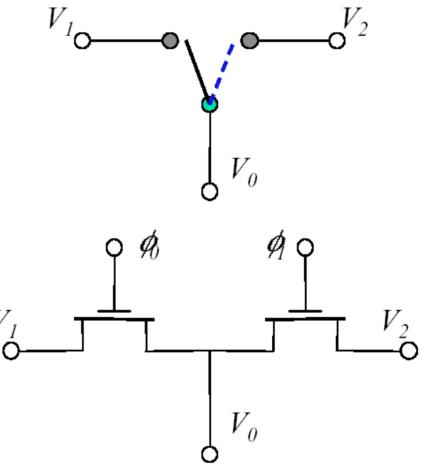

#### Switched-Capacitor Fundamentals

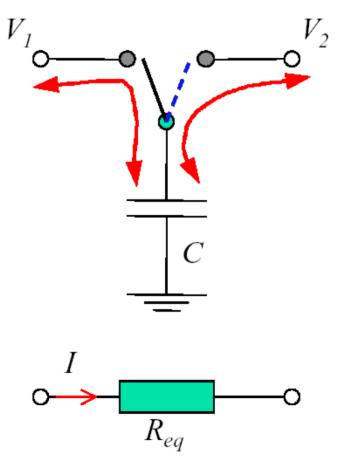

• A switched capacitor simulates a resistor

$$q(t) = C \cdot V_1$$

$$q(t + \tau) = C \cdot V_2$$

$$\Delta q(t) = C \cdot (V_1 - V_2)$$

$$I = \Delta q(t) / T = C \cdot (V_1 - V_2) / T$$

$$R_{eq} = T/C$$

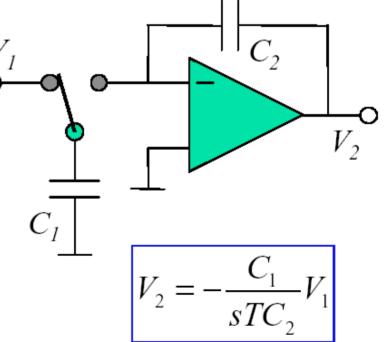

#### First (Poor) SC Integrator

- Use the active-RC integrator and replace the resistor with a switched capacitor

- Capacitor ratio determines the transfer function

- Improved matching

- Low power possible

#### Charge Redistribution Analysis

- Consider the charge transportation

- OP outputs can take/give charge

- OP (CMOS) inputs cannot take/give charge

- Equilibrium will take place after settling

- No charge can disappear from an unconnected capacitor plate

- A capacitor with both plates connected to same potential will lose all of its charge

#### Charge Redistribution Analysis

- Investigate both clock phases and denote the initial conditions in each phase

- Investigate the charge conservation and find the transfer function

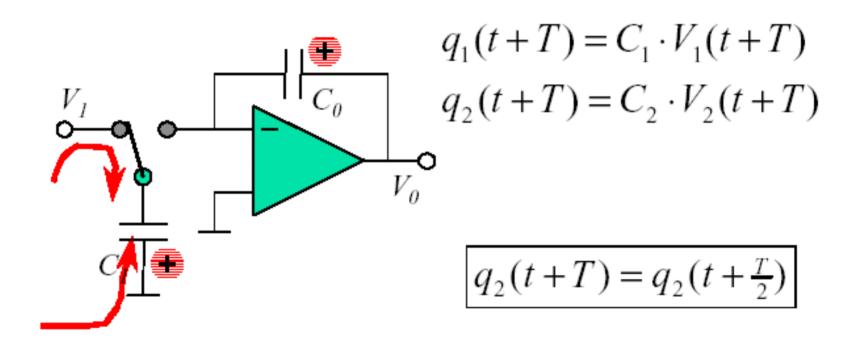

# Charge Redistribution Analysis • At t = t $\begin{vmatrix} q_1(t) = C_1 \cdot V_1(t) \\ q_2(t) = C_2 \cdot V_2(t) \end{vmatrix}$

Denote reterences on the capacitors

#### Charge Redistribution Analysis

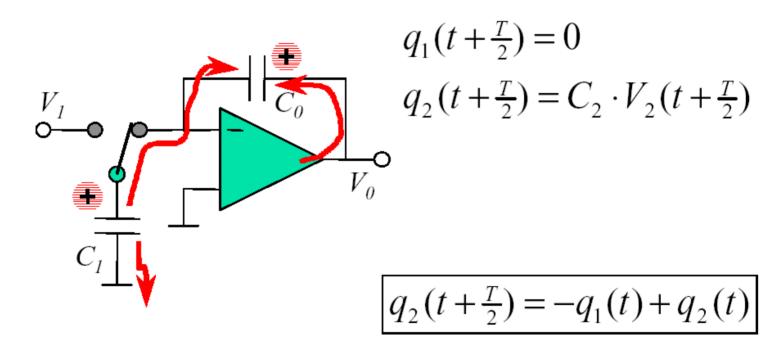

• At t = t + T/2

• CI loses its charge to ground and C0

#### Charge Redistribution Analysis

- At t = t+T

• Charge conservation.

Transfer Function

$$q_{2}(t+T) = q_{2}(t+\frac{T}{2}) = -q_{1}(t) + q_{2}(t)$$

$$C_{2} \cdot V_{2}(t+T) = C_{2} \cdot V_{2}(t) - C_{1} \cdot V_{1}(t)$$

$$C_{2} \cdot V_{2}(z) \cdot z = C_{2} \cdot V_{2}(z) - C_{1} \cdot V_{1}(z) \Rightarrow$$

$$C_{2} \cdot V_{2}(z) \cdot (z-1) = -C_{1} \cdot V_{1}(z) \Rightarrow$$

$$H(z) = \frac{V_{2}(z)}{V_{1}(z)} = -\frac{C_{1}}{C_{2}} \cdot \frac{1}{z-1} = -\frac{C_{1}}{C_{2}} \cdot \frac{z^{-1}}{1-z^{-1}}$$

Herefore Discrete time Integrator

Inverting Discrete-time Integrator

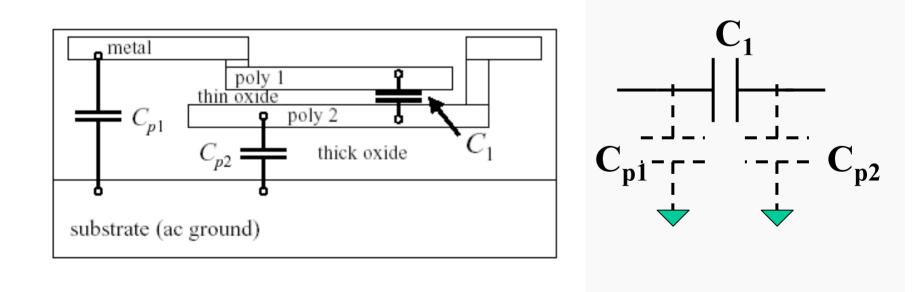

Influence of Parasitic Capacitors

$C_{p2} \sim 20\% C_1!!$

• Parasitic from fringing capacitors and bottom-plate to substrate

#### Parasitic Capacitance

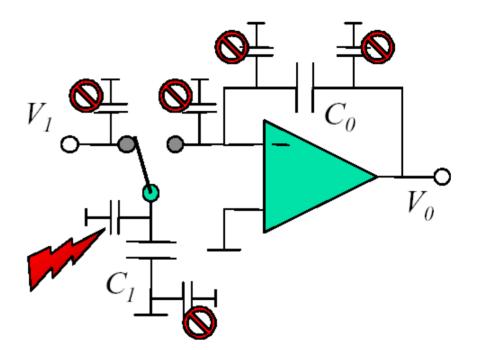

- Include parasitic to all capacitors, switches, etc.

- Remove those who do not effect the transfer function

### $q_2(t+T) = q_2(t+\frac{T}{2}) = -q_1(t) + q_2(t)$ $C_2 \cdot V_2(t+T) = -C_2 \cdot V_2(t) + (C_1 + C_p) \cdot V_1(t)$ $C_2 \cdot V_2(z) \cdot z = C_2 \cdot V_2(z) - (C_1 + C_p) \cdot V_1(z) \Rightarrow$ $C_2 \cdot V_2(z) \cdot (z-1) = -(C_1 + C_p) \cdot V_1(z) \Longrightarrow$ $H(z) = \frac{V_2(z)}{V_1(z)} = -\frac{C_1 + C_p}{C_2} \cdot \frac{1}{z - 1} = -\frac{C_1 + C_p}{C_2} \cdot \frac{z^{-1}}{1 - z^{-1}}$

**Transfer Function**

• Gain is affected by the parasitic.

Parasitic Capacitors - Conclusions

Parasitic insensitive vs. sensitive

- To minimize the influence of parasitic:

- Switch the capacitor between a voltage source and ground

- Switch the capacitor between ground and virtual ground

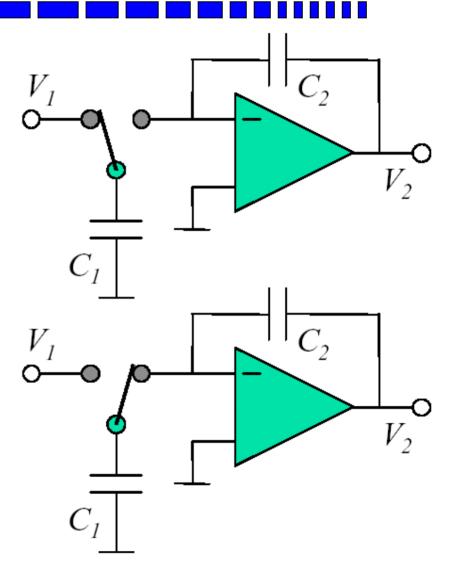

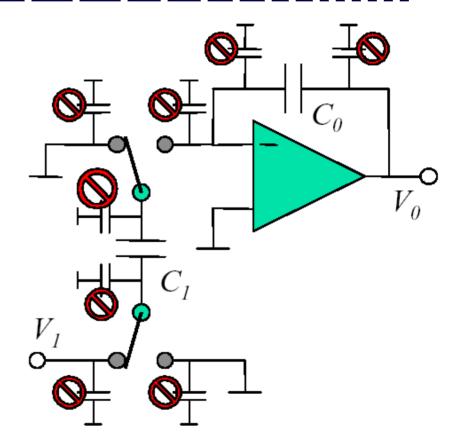

#### Parasitic Insensitive SC Circuits

#### Parasitic Insensitive SC Circuits

- Include parasitic to all capacitors, switches, etc.

- Remove those

who do not

effect the

transfer function.

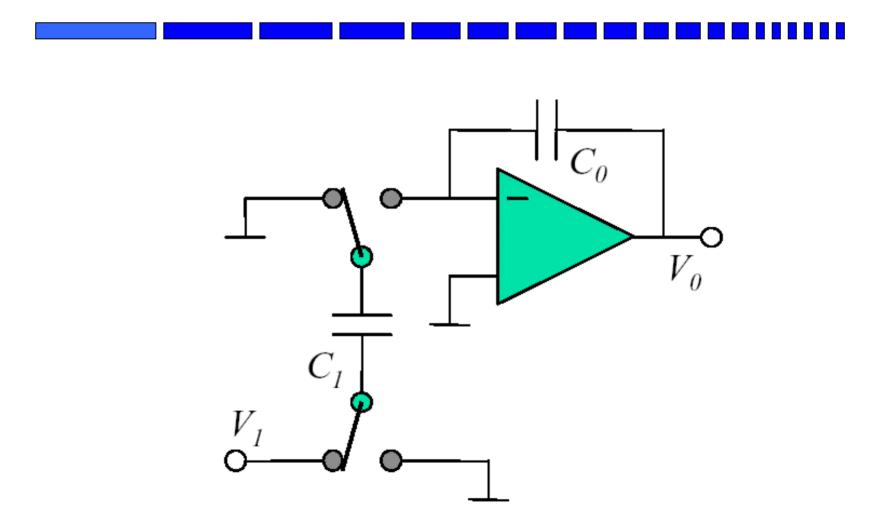

# Charge Redistribution Analysis • At t = t $C_{o}$ $V_{0}$ $\begin{vmatrix} q_1(t) = C_1 \cdot V_1(t) \\ q_2(t) = C_2 \cdot V_2(t) \end{vmatrix}$

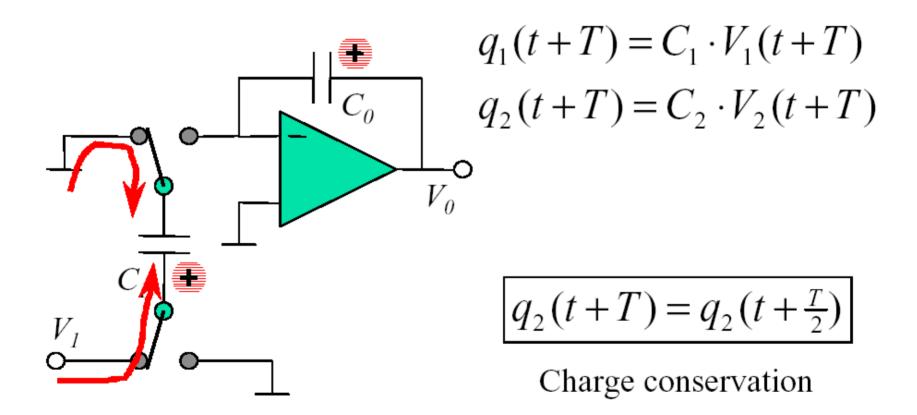

Dr. Hongjiang Song, Arizona State University

## Charge Redistribution Analysis • At t = t + T/2 $q_1(t+\frac{T}{2}) = 0$ $q_2(t + \frac{T}{2}) = C_2 \cdot V_2(t + \frac{T}{2})$ $q_2(t + \frac{T}{2}) = q_1(t) + q_2(t)$ $C_1$ loses its charge to ground and $C_2$ .

#### Charge Redistribution Analysis

• At t = t + T

### **Transfer Function** $q_2(t+T) = q_2(t+\frac{T}{2}) = q_1(t) + q_2(t)$ $C_{2} \cdot V_{2}(t+T) = C_{2} \cdot V_{2}(t) + C_{1} \cdot V_{1}(t)$ $C_2 \cdot V_2(z) \cdot z = C_2 \cdot V_2(z) + C_1 \cdot V_1(z) \Longrightarrow$ $C_2 \cdot V_2(z) \cdot (z-1) = C_1 \cdot V_1(z) \Longrightarrow$ $H(z) = \frac{V_2(z)}{V_1(z)} = \frac{C_1}{C_2} \cdot \frac{1}{z - 1} = \frac{C_1}{C_2} \cdot \frac{z^{-1}}{1 - z^{-1}}$

Discrete-time Integrator

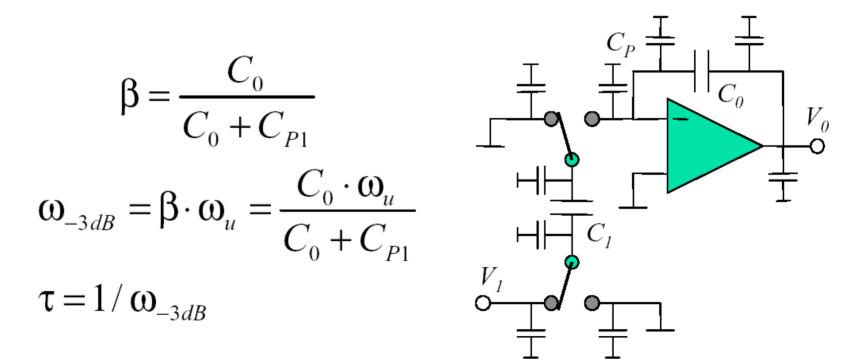

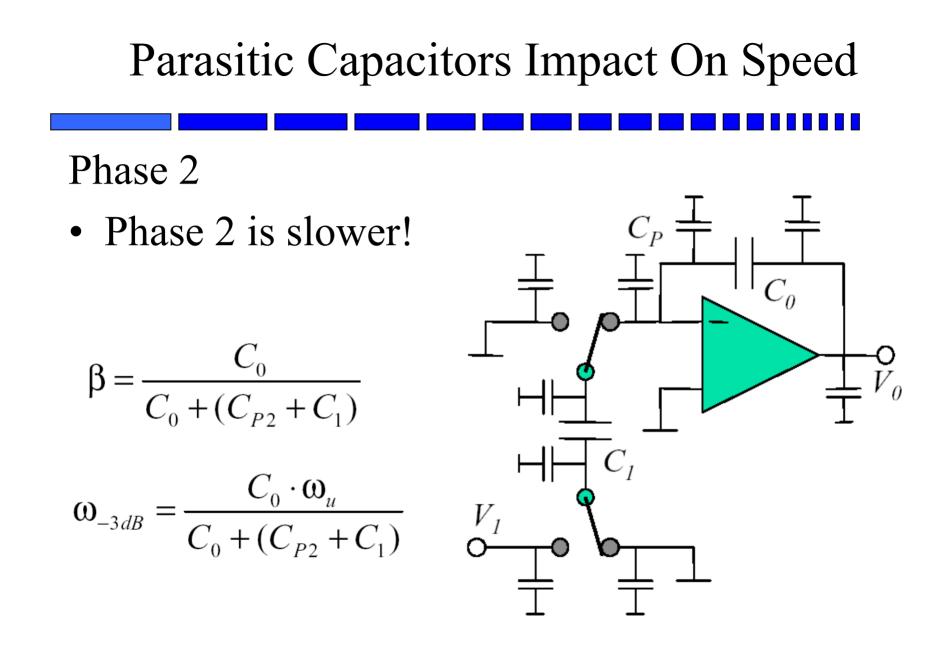

Parasitic Capacitors Impact On Speed

- Both clock phases have to be investigated!

- Parasitic may influence the speed although the transfer function is not effected.

- Consider the feedback factor in each phase.

(Feedback factor, β, is the amount of output signal fed back to the input, typically voltage divider).

### Parasitic Capacitors Impact On Speed Phase 1

• The parasitic affect the load capacitance

Dr. Hongjiang Song, Arizona State University

#### Switches in SC Circuits

- Realized with NMOS transistors

- To increase speed

- To reduce size

- RC-timing!

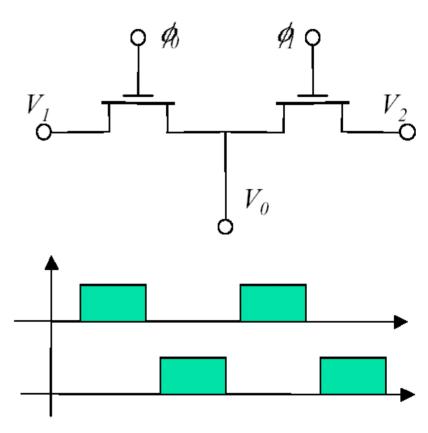

#### Switches In SC Circuits

- Non-overlapping clock-phases

- Guarantee that the two NMOS transistors, cannot conduct at the,same time

- Reduces charge leakage

#### Switches In SC Circuits

- Clock Feedthrough (CFT)

- CFT affects the transfer function

- Use small MOS switches

- CFT Cancellation Techniques

- Channel charge injection

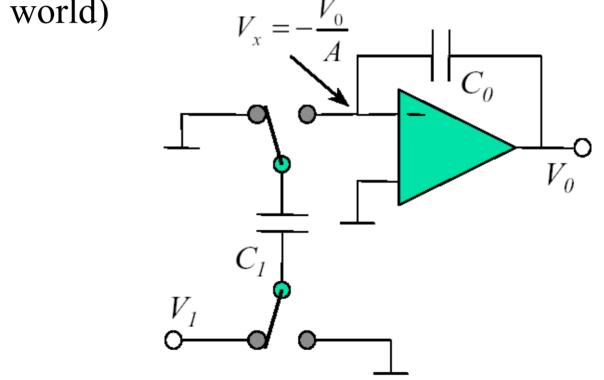

#### Influence of Non-Ideal OP

- Finite gain.

- Assume the OP has a finite gain, A, (as in the real world)  $V = -\frac{V_0}{V_0}$

#### Influence of Finite Gain OP

$$\begin{cases} q_1(t) = C_1 \cdot V_1(t) \\ q_2(t) = C_2 \cdot (V_2(t) - (-V_2(t) \cdot \frac{1}{A})) \end{cases}$$

$$\begin{cases} q_1(t + \frac{T}{2}) = -C_1 \cdot \left(-V_2(t + \frac{T}{2}) \cdot \frac{1}{A}\right) \\ q_2(t + \frac{T}{2}) = C_2 \cdot V_2(t + \frac{T}{2}) \cdot \left(1 + \frac{1}{A}\right) \end{cases}$$

$$\begin{aligned} q_2(t + \frac{T}{2}) + q_1(t + \frac{T}{2}) &= q_1(t) + q_2(t) \\ q_2(t + T) &= q_2(t + \frac{T}{2}) \Longrightarrow V_2(t + \frac{T}{2}) = V_2(t) \\ C_2 \cdot V_2(t + T) \cdot (1 + \frac{1}{4}) &= C_1 \cdot V_1(t) + C_2 \cdot V_2(t) \cdot (1 + \frac{1}{4}) - C_1 \cdot V_2(t + T) \cdot \frac{1}{4} \end{aligned}$$

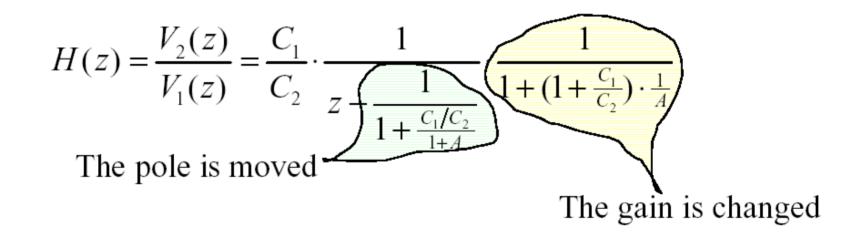

# Influence of Finite Gain OP

$\begin{aligned} C_2 \cdot V_2(z) \cdot z \cdot (1 + \frac{1}{A}) &= C_1 \cdot V_1(z) + C_2 \cdot V_2(z) \cdot (1 + \frac{1}{A}) - C_1 \cdot V_2(z) \cdot z \cdot \frac{1}{A} \\ V_2(z) \cdot (C_2 \cdot z \cdot (1 + \frac{1}{A}) - C_2 \cdot (1 + \frac{1}{A}) - C_1 \cdot z \cdot \frac{1}{A}) &= C_1 \cdot V_1(z) \end{aligned}$

• Lossy Integrator!

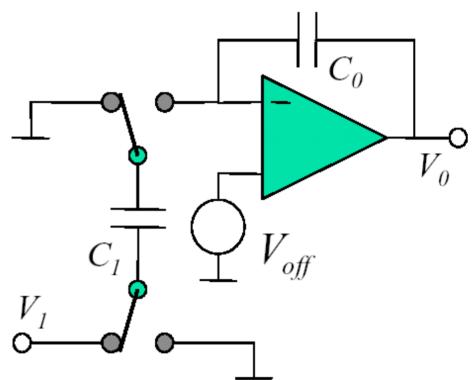

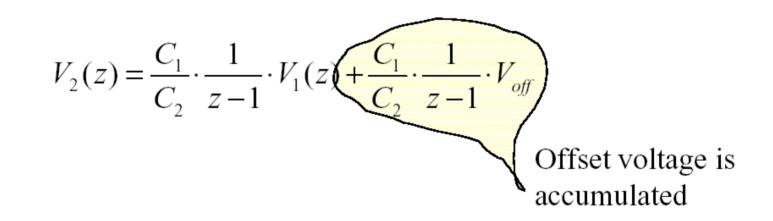

#### Influence of OP Offset Voltage

- Input offset voltage.

- Matching errors can be modeled as a voltage source, Voff, at the input of the OP.

#### Influence of OP Offset Voltage

$$\begin{cases} q_1(t) = C_1 \cdot V_1(t) \\ q_2(t) = C_2 \cdot (V_2(t) - V_{off}) \end{cases}$$

$$\begin{cases} q_1(t+\frac{T}{2}) = -C_1 \cdot V_{off} \\ q_2(t+\frac{T}{2}) = C_2 \cdot \left(V_2(t+\frac{T}{2}) \cdot V_{off}\right) \end{cases}$$

$$\begin{split} & q_2(t + \frac{T}{2}) + q_1(t + \frac{T}{2}) = q_1(t) + q_2(t) \\ & q_2(t + T) = q_2(t + \frac{T}{2}) \Longrightarrow V_2(t + \frac{T}{2}) = V_2(t) \\ & C_2 \cdot (V_2(t + T) - V_{off}) = C_1 \cdot V_1(t) + C_2 \cdot (V_2(t) - V_{off}) + C_1 \cdot V_{off} \\ & C_2 \cdot V_2(t + T) = C_1 \cdot V_1(t) + C_2 \cdot V_2(t) + C_1 \cdot V_{off} \end{split}$$

### Influence of OP Offset Voltage

#### $C_2 \cdot V_2(z) \cdot z = C_1 \cdot V_1(z) + C_2 \cdot V_2(z) + C_1 \cdot V_{off}$

• We need an SC circuit with offset compensation technique. That circuit must have a so called auto-zeroing phase.